Understanding the Essence of UVM RAL

As we embark on the intricate journey of UVM (Universal Verification Methodology), a critical aspect that demands meticulous exploration is the UVM Register Abstraction Layer (RAL). In this comprehensive article, we delve deep into the core of UVM RAL, unraveling its intricacies, architecture, and real-world applications.

The Fundamental Need for UVM RAL

In any complex digital design, registers play a pivotal role, serving as the interface between hardware and software. Whether it's control registers steering the functionality of the design or status registers providing insights into its operational state, managing these registers efficiently is paramount. This is precisely where UVM RAL steps in, offering an abstraction layer that models and encapsulates the intricacies of design registers.

Anatomy of UVM RAL: A Structural Overview

At the heart of UVM RAL lies a well-organized hierarchical structure, a blueprint that mirrors the memory, registers, and address maps into coherent address blocks. Each register boasts its own class, and within these classes, fields are created and configured. This hierarchical arrangement provides a systematic representation of the design's register layout, paving the way for efficient verification.

Register Model Implementation

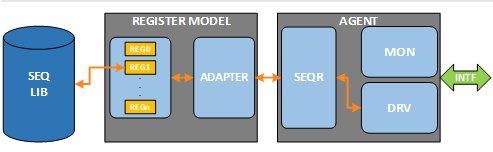

To better grasp the UVM RAL structure, let's visualize it in the context of the broader verification environment. The user guide provides a helpful depiction (Fig. 1), showcasing the register model relative to the rest of the UVM environment.

A noteworthy element in this structure is the 'Generator' bubble. In modern designs housing hundreds or even thousands of registers and fields, manual creation of SystemVerilog code becomes a daunting task. This is where generators come into play. They automatically generate the equivalent register model in SystemVerilog code based on the register specifications provided in a design spreadsheet.

UVM RAL Workflow: From Model to Adapter

How does the UVM RAL workflow unfold? Let's break it down:

-

Building the Register Model:

- The register model is constructed using a meticulously organized hierarchical structure, capturing memory, registers, and address maps within address blocks.

- Each register and its fields are encapsulated within their respective classes.

class my_register_class extends uvm_reg; // ... (Register class implementation) endclass : my_register_class -

Organizing Registers into Blocks:

- Registers are then organized into blocks, accompanied by the declaration of a register map that organizes registers based on their designated addresses.

class my_register_block extends uvm_reg_block; // ... (Register block implementation) endclass : my_register_class -

Adapter Creation in the Agent:

- An adapter acts as a bridge between the model and lower levels, facilitating abstraction.

- It converts register model transactions to lower-level bus transactions and vice versa.

class my_register_adapter extends uvm_reg_adapter; // ... (Register adapter implementation) endclass : my_register_adapter -

Predictor Interaction:

- The predictor receives information from the monitor, ensuring changes in values in the DUT registers are reflected back to the register model.

typedef uvm_reg_predictor#(my_transaction_class) my_reg_predictor; -

Complete Structure Overview:

- The overall structure, as depicted in Figure 5, showcases the interconnected elements of the register model within the broader UVM testbench.

Beyond Registers: Modeling Memory in UVM RAL

While the focus so far has been on registers, the versatility of UVM RAL extends to modeling memory as well. The structural representation incorporates a memory module within the model, opening avenues for a more comprehensive verification approach.

Generating Stimulus: Register Access API

With the register model in place, the next logical step is generating stimulus. Register access is orchestrated through the register API, where methods like write() and read() are called from a sequence. This initiates the flow of data through the register model to the sequencer, driver, and ultimately to the DUT. The monitor captures any activity, relaying it back to the predictor. Subsequently, the predictor sends the data to the adapter, where the bus data undergoes conversion to a register model format, updating the register model value through a predict() method call.

UVM RAL Sequences: Orchestrating Register Access

Sequences play a pivotal role in UVM RAL, housing the method calls for register access. In the example below, a sequence is created to call the write() and read() APIs, causing the movement of data.

class my_register_sequence extends uvm_reg_sequence;

// ... (Sequence implementation)

endclass : my_register_sequence

The block is declared within sequences, and registers are referenced hierarchically in the body task to call write() and read(). Additional methods like peek() and poke() facilitate individual field accesses, enriching the array of options for register manipulation.

A Glimpse Into UVM RAL: A Closing Note

While this article provides a detailed overview of UVM RAL, it's important to acknowledge that there's more to explore. The intent is to demystify the fundamental concepts and showcase the structured approach that UVM RAL brings to register modeling. To truly master UVM RAL, dive into additional reading, browse examples, and engage in practical application.

As you navigate the realm of UVM Register Model and Layer, consider these resources for further insights:

-

Verification Academy's UVM Register Layer Guide:

-

Design And Reuse Article on UVM RAL Model: Usage and Application:

This exploration serves as a compass, guiding you through the complexities of UVM RAL. May your journey into UVM verification be enriched with newfound understanding and proficiency in harnessing the power of the UVM Register Abstraction Layer. Until the next exploration, happy coding and testing!

No comments yet