In the intricate realm of embedded systems, the synergy of a robust UVM (Universal Verification Methodology) testbench and a well-defined UVM Register Model stands as a linchpin in achieving functional safety and security. This article navigates through the intricacies of UVM, provides an illustrative example of a UVM Register Model, and explores the critical role these elements play in fortifying embedded systems against potential vulnerabilities.

UVM Testbench: Cornerstone of Verification Efficiency:

The UVM Testbench serves as the cornerstone of efficient verification methodologies in the design and validation of embedded systems. UVM, based on SystemVerilog, provides a standardized framework for verification that fosters reusability, scalability, and maintainability.

At its core, a UVM Testbench encapsulates verification components, sequences, and environments that collectively verify the functionality of the design under test (DUT). By adopting a methodology that promotes modularization and reuse, UVM significantly enhances the efficiency and effectiveness of the verification process.

UVM Register Model: Mapping Hardware Registers to Software:

In the pursuit of functional safety and security, the UVM Register Model emerges as a crucial component. This model acts as a bridge between the hardware design and the software that interacts with it. It provides a standardized representation of the registers within the DUT, facilitating seamless communication between the verification environment and the actual hardware.

A UVM Register Model typically includes register definitions, field information, and methods to read and write to these registers. This abstraction allows verification engineers to create scenarios that mimic real-world interactions with the hardware, ensuring that the DUT behaves as expected under different conditions.

Example of a UVM Register Model:

Let's consider a simple example to illustrate the essence of a UVM Register Model. Assume we have a DUT with a configuration register controlling a safety-critical functionality, such as a temperature sensor threshold. The UVM Register Model for this scenario might look like this:

systemverilogclass DUT_Configuration_Regs extends uvm_reg_block;

// Configuration register definition

uvm_reg_field threshold_enable;

uvm_reg_field temperature_threshold;

// Constructor

function new(string name = "DUT_Configuration_Regs");

super.new(name, UVM_NO_COVERAGE);

// Define configuration register and fields

threshold_enable = uvm_reg_field::type_id::create("threshold_enable",, this);

temperature_threshold = uvm_reg_field::type_id::create("temperature_threshold",, this);

endfunction

endclass

In this simplistic example, DUT_Configuration_Regs represents the block of registers associated with the DUT's configuration. It includes fields for enabling the temperature threshold and setting the actual threshold value.

Functional Safety and Security Integration:

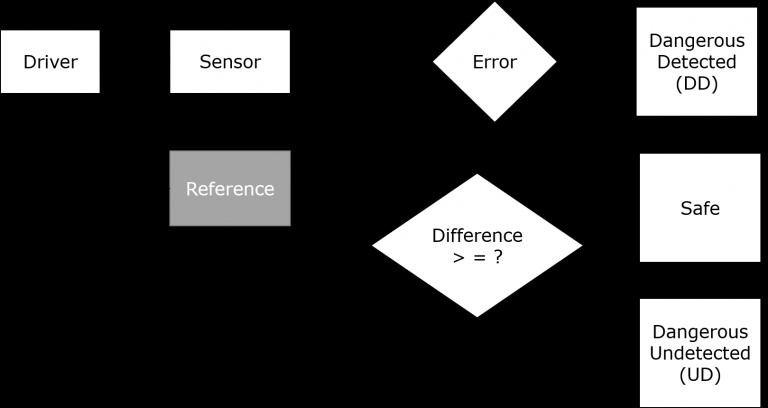

Integrating UVM Testbench and Register Models into the broader context of functional safety and security is a strategic imperative. Verification scenarios designed within the UVM framework allow engineers to rigorously test the safety-critical aspects of the DUT. By utilizing the UVM Register Model, verification engineers can ensure that the hardware registers, especially those governing safety parameters, are behaving as specified.

Moreover, security considerations involve verifying that the DUT is resilient to potential exploits or unauthorized access. The UVM Testbench, with its flexibility and scalability, enables the creation of scenarios that stress different aspects of security, ensuring that the embedded system can withstand external threats.

Conclusion: Harnessing UVM for Enhanced Embedded System Reliability:

In the evolving landscape of embedded systems, where functionality, safety, and security are paramount, leveraging UVM Testbench and UVM Register Models becomes indispensable. The standardized and modular approach offered by UVM not only enhances verification efficiency but also provides a robust framework for ensuring the reliability and resilience of embedded systems.

By incorporating safety-critical aspects into the UVM Register Model Example and designing comprehensive test scenarios, engineers can navigate the complexities of modern embedded designs with precision. The synergy of UVM in both the verification and register modeling domains empowers developers to meet stringent functional safety and security standards, ensuring that embedded systems not only operate flawlessly but also stand resilient against potential vulnerabilities.

No comments yet