The Significance of the Register Model in UVM

Introduction

In the field of hardware verification, the Universal Verification Methodology (UVM) is a powerful framework that provides a systematic and standardized method for digital design verifica...

18 April

·

0

· 1

·

Agni Sys

5 Reasons for Using an Open Source Register Automation Tool | Agnisys

Register automation is an integral part of IP and SoC development. Long ago, design, verification, firmware, and documentation teams preferred doing register management manually or each tea...

18 April

·

0

· 1

·

Agni Sys

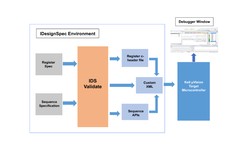

CMSIS support in IDesignSpec | Agnisys

IDesignSpecTM (IDS) is a product suite that improves the productivity of FPGA/ASIC, IP/SoC, and System Development teams. These products encompass an innovative register information manag...

07 March

·

0

· 1

·

Agni Sys

Formal Verification through ARV™-Formal

In the dynamic landscape of Very Large Scale Integration (VLSI) design, the ever-growing complexity of Application-Specific Integrated Circuits (ASICs) has posed significant challenges to the traditio...

20 February

·

0

· 1

·

Agni Sys

Too Many Iterations? How to Avoid Three Common Problems in Semiconductor Design

Developing semiconductor intellectual property (IP), system-on-chip (SoC) designs, and complete systems is enormously challenging. Even a small error in the hardware design can require a very expensiv...

20 February

·

0

· 1

·

Agni Sys

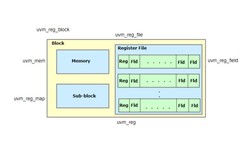

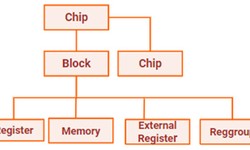

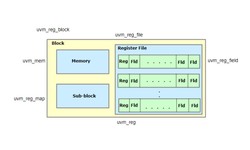

Deep Dive into UVM Register Model | Agnisys Technology

UVM Register Model, a key component of the Universal Verification Methodology (UVM), is a standardized methodology for verifying digital designs. It provides a framework for creating robust and r...

30 January

·

0

· 1

·

Agni Sys

IP-XACT | Efficient IP and SoC Building with IP-XACT: Streamlined Strategies

Chip designers have always reused circuitry, when possible, to shrink the project schedule, save resources, and reduce risk by using a silicon-verified design. Many types of chip design ...

23 January

·

0

· 1

·

Agni Sys