In the intricate domain of System-on-Chip (SoC) design and verification, the Universal Verification Methodology (UVM) Register holds a central position, defining the communication interface between design and verification components. This article aims to unravel the dynamics of UVM Register and shed light on the transformative influence of the Register Model Generator, a cutting-edge tool that propels the next generation of SoC automation.

UVM Register: A Cornerstone of Verification Precision

UVM Register, at its essence, serves as the linchpin in the verification process, offering a standardized abstraction for hardware registers within an SoC. Its primary role is to ensure the consistent and accurate behavior of registers across diverse scenarios, fostering a robust foundation for verification engineers.

The Evolution of UVM Register Model

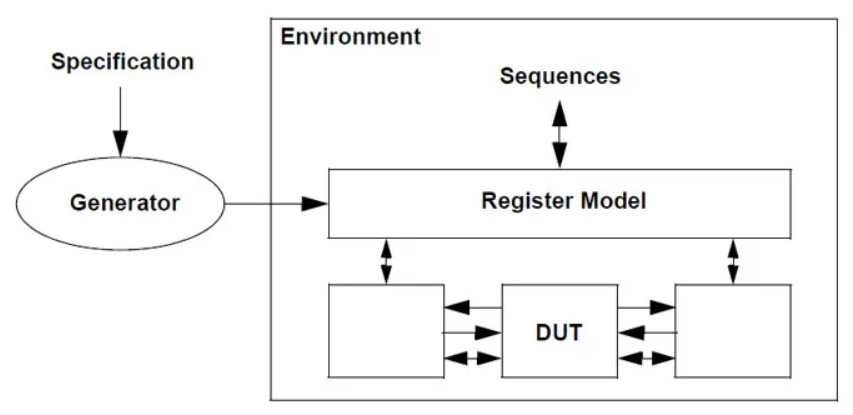

The UVM Register Model extends the capabilities of UVM Register by providing a hierarchical framework that mirrors the organization of registers within the SoC design. This comprehensive model not only simplifies the verification task but also enhances reusability and maintainability, crucial aspects in the ever-demanding landscape of chip design.

Register Model Generator: A Paradigm Shift in Automation

At the forefront of innovation, the Register Model Generator emerges as a game-changer in SoC design and verification. This tool automates the creation of UVM Register Models, offering a host of advantages that redefine the efficiency and accuracy benchmarks in the industry.

Streamlining Development Efforts

The Register Model Generator accelerates the UVM Register Model creation process, drastically reducing the manual effort required. This accelerated development pace proves indispensable in meeting tight project deadlines without compromising on the quality of the verification process.

Precision through Automation

By minimizing the risk of human error, the Register Model Generator ensures the generated models align seamlessly with the design specifications. This precision not only enhances the reliability of verification results but also instills confidence in the overall design integrity.

Unleashing Reusability Potential

Teams can leverage the Register Model Generator to effortlessly reuse models across various projects. This not only translates to time savings but also establishes a consistent and standardized approach to UVM Register Models, fostering collaboration and knowledge transfer within and across teams.

Integration for Seamless Workflows

The tool seamlessly integrates into existing design and verification workflows, enhancing overall efficiency. Its compatibility ensures that design and verification teams can readily adopt the Register Model Generator without disrupting established processes, thereby facilitating a smooth transition.

Charting the Course Forward

As we navigate the complex terrain of SoC design, the synergy between UVM Register, UVM Register Model, and the Register Model Generator emerges as a critical enabler for success. This trio not only simplifies the verification process but also sets the stage for future advancements in automation and precision.

In conclusion, the Register Model Generator stands as a beacon of progress, ushering in a new era where automation takes center stage in UVM Register Model generation. The journey of SoC design and verification continues to evolve, and with tools like the Register Model Generator, the industry is well-equipped to meet the challenges of tomorrow head-on.

No comments yet